# TC500/A/510/514

### **Precision Analog Front Ends**

#### Features:

- Precision (up to 17 bits) A/D Converter "Front End"

- 3-Pin Control Interface to Microprocessor

- Flexible: User Can Trade-off Conversion Speed for Resolution

- Single-Supply Operation (TC510/TC514)

- 4 Input, Differential Analog MUX (TC514)

- Automatic Input Voltage Polarity Detection

- Low Power Dissipation:

- (TC500/TC500A): 10 mW

- (TC510/TC514): 18 mW

- Wide Analog Input Range:

- ±4.2V (TC500A/TC510)

- Directly Accepts Bipolar and Differential Input Signals

#### **Applications:**

- Precision Analog Signal Processor

- Precision Sensor Interface

- High Accuracy DC Measurements

#### **General Description:**

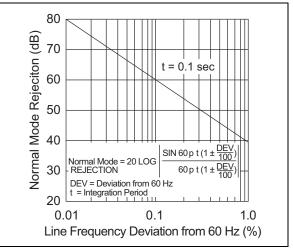

TheTC500/A/510/514 family are precision analog front ends that implement dual slope A/D converters having a maximum resolution of 17 bits plus sign. As a minimum, each device contains the integrator, zero crossing comparator and processor interface logic. The TC500 is the base (16-bit max) device and requires both positive and negative power supplies. The TC500A is identical to the TC500 with the exception that it has improved linearity, allowing it to operate to a maximum resolution of 17 bits. The TC510 adds an onboard negative power supply converter for singlesupply operation. The TC514 adds both a negative power supply converter and a 4-input differential analog multiplexer.

Each device has the same processor control interface consisting of 3 wires: control inputs (A and B) and zerocrossing comparator output (CMPTR). The processor manipulates A, B to sequence the TC5XX through four phases of conversion: auto-zero, integrate, de-integrate and integrator zero. During the auto-zero phase, offset voltages in the TC5XX are corrected by a closed loop feedback mechanism. The input voltage is applied to the integrator during the integrate phase. This causes an integrator output dv/dt directly proportional to the magnitude of the input voltage. The higher the input voltage, the greater the magnitude of the voltage stored on the integrator during this phase. At the start of the de-integrate phase, an external voltage reference is applied to the integrator and, at the same time, the external host processor starts its on-board timer. The processor maintains this state until a transition occurs on the CMPTR output, at which time the processor halts its timer. The resulting timer count is the converted analog data. Integrator zero (the final phase of conversion) removes any residue remaining in the integrator in preparation for the next conversion.

The TC500/A/510/514 offer high resolution (up to 17 bits), superior 50/60 Hz noise rejection, low-power operation, minimum I/O connections, low input bias currents and lower cost compared to other converter technologies having similar conversion speeds.

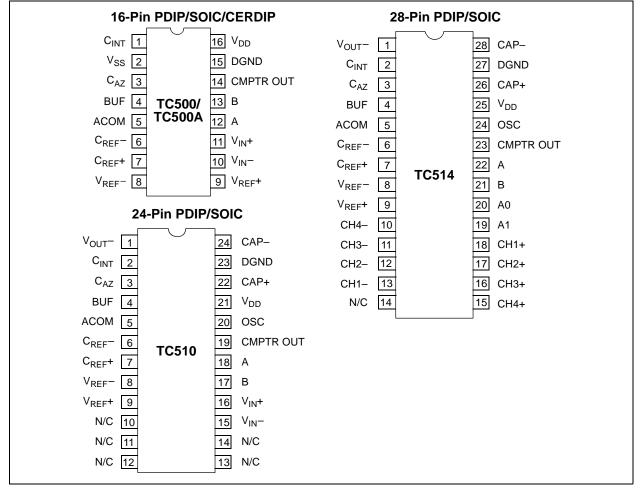

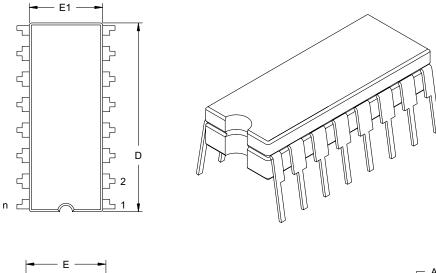

#### Package Types

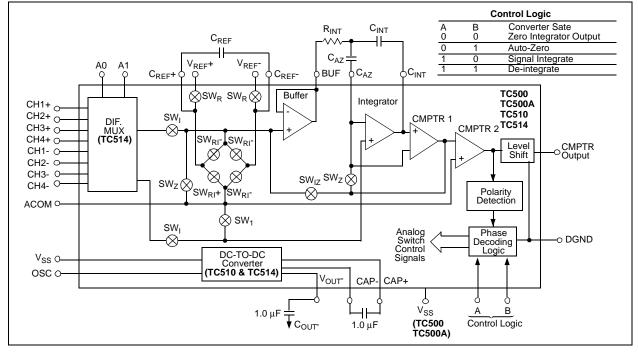

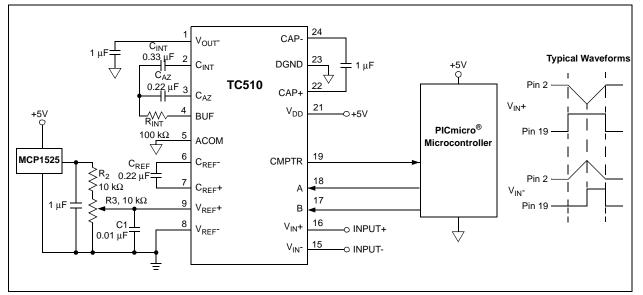

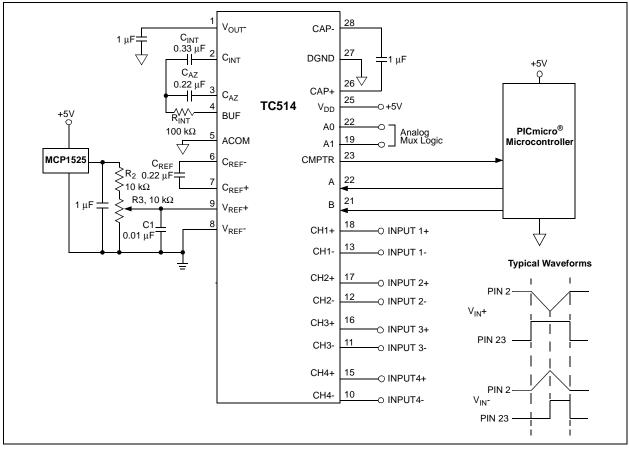

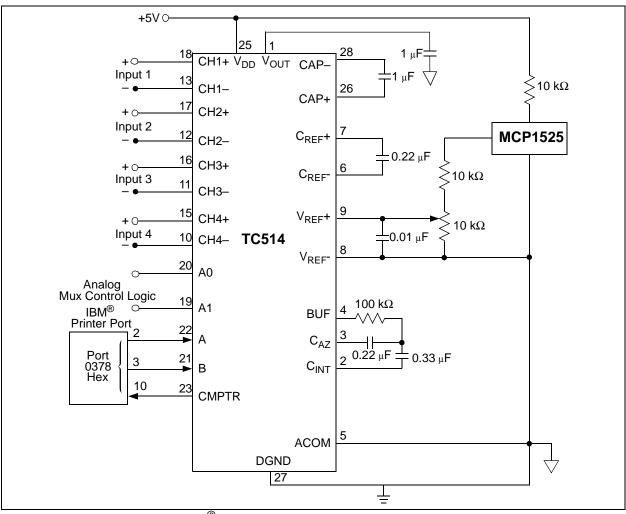

#### **Typical Application**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings†**

| TC510/TC514 Positive Supply Voltage<br>(V <sub>DD</sub> to GND)+10.5V                           |

|-------------------------------------------------------------------------------------------------|

| TC500/TC500A Supply Voltage                                                                     |

| $(V_{DD} \text{ to } V_{SS}) \dots + 18V$                                                       |

| TC500/TC500A Positive Supply Voltage                                                            |

| (V <sub>DD</sub> to GND)+12V                                                                    |

| TC500/TC500A Negative Supply Voltage                                                            |

| (V <sub>SS</sub> to GND)8V                                                                      |

| Analog Input Voltage (V <sub>IN</sub> + or V <sub>IN</sub> -)V <sub>DD</sub> to V <sub>SS</sub> |

| Logic Input VoltageV <sub>DD</sub> +0.3V to GND - 0.3V                                          |

| Voltage on OSC:                                                                                 |

| 0.3V to (V <sub>DD</sub> +0.3V) for V <sub>DD</sub> < 5.5V                                      |

| Ambient Operating Temperature Range:                                                            |

| 0°C to +70°C                                                                                    |

| Storage Temperature Range:65°C to +150°C                                                        |

**†** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### DC CHARACTERISTICS

Electrical Specifications: Unless otherwise specified, TC510/TC514:  $V_{DD}$  = +5V, TC500/TC500A:  $V_{SS}$  = ±5V.  $C_{AZ}$  =  $C_{REF}$  = 0.47  $\mu$ F.

| Demonstration                                 |                  | T <sub>A</sub> = +25°C |       |                       | T <sub>A</sub> =      | 0°C to 7 | 70°C                  |        | <b>o</b> 197                                                                |  |

|-----------------------------------------------|------------------|------------------------|-------|-----------------------|-----------------------|----------|-----------------------|--------|-----------------------------------------------------------------------------|--|

| Parameters                                    | Sym              | Min. Typ. Max.         |       | Min. Typ. Max.        |                       | Units    | Conditions            |        |                                                                             |  |

| Analog                                        |                  |                        |       |                       |                       |          |                       |        |                                                                             |  |

| Resolution                                    |                  | 60                     |       | _                     | _                     | _        | _                     | μV     | Note 1                                                                      |  |

| Zero-scale Error with                         | ZSE              | —                      |       | 0.005                 | _                     | 0.005    | 0.012                 | % F.S. | TC500/TC510/TC514                                                           |  |

| Auto-zero Phase                               |                  | —                      | —     | 0.003                 | —                     | 0.003    | 0.009                 |        | TC500A                                                                      |  |

| End Point Linearity                           | ENL              | —                      | 0.005 | 0.015                 | _                     | 0.015    | 0.060                 | % F.S. | TC500/TC510/TC514                                                           |  |

|                                               |                  | —                      | —     | 0.010                 | —                     | 0.010    | 0.045                 | % F.S. | Note 1, Note 2,<br>TC500A                                                   |  |

| Best-Case Straight<br>Line Linearity          | NL               | —                      | 0.003 | 0.008                 | _                     |          | —                     | % F.S. | TC500/TC510/TC514,<br>Note 1, Note 2                                        |  |

|                                               |                  | _                      |       | 0.005                 | _                     | _        | _                     | % F.S. | TC500A                                                                      |  |

| Zero-scale Temp.<br>Coefficient               | ZS <sub>TC</sub> | —                      | —     | —                     | _                     | 1        | 2                     | μV/°C  | Over Operating<br>Temperature Range                                         |  |

| Full-scale Symmetry<br>Error (Rollover Error) | SYE              | —                      | 0.01  | —                     | _                     | 0.03     | —                     | % F.S. | Note 1                                                                      |  |

| Full-scale<br>Temperature<br>Coefficient      | FS <sub>TC</sub> | _                      | _     | —                     | _                     | 10       | —                     | ppm/°C | Over Operating<br>Temperature Range;<br>External Reference<br>TC = 0 ppm/°C |  |

| Input Current                                 | I <sub>IN</sub>  | —                      | 6     | _                     | _                     | —        | _                     | pА     | $V_{IN} = 0V$                                                               |  |

| Common Mode<br>Voltage Range                  | V <sub>CMR</sub> | V <sub>SS</sub> + 1.5  | —     | V <sub>DD</sub> – 1.5 | V <sub>SS</sub> + 1.5 | _        | V <sub>DD</sub> – 1.5 | V      |                                                                             |  |

| Integrator Output<br>Swing                    |                  | V <sub>SS</sub> + 0.9  | —     | V <sub>DD</sub> - 0.9 | V <sub>SS</sub> + 0.9 |          | V <sub>SS</sub> + 0.9 | V      |                                                                             |  |

| Analog Input Signal<br>Range                  |                  | V <sub>SS</sub> + 1.5  | —     | V <sub>DD</sub> – 1.5 | V <sub>SS</sub> + 1.5 |          | V <sub>SS</sub> + 1.5 | V      | ACOM = GND = 0V                                                             |  |

Note 1: Integrate time  $\ge 66$  msec, auto-zero time  $\ge 66$  msec, V<sub>INT</sub> (peak)  $\approx 4V$ .

**2:** End point linearity at  $\pm 1/4$ ,  $\pm 1/2$ ,  $\pm 3/4$  F.S. after full-scale adjustment.

3: Rollover error is related to  $C_{INT}$ ,  $C_{REF}$ ,  $C_{AZ}$  characteristics.

#### **DC CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Unless otherwise specified, **TC510/TC514**:  $V_{DD} = +5V$ , **TC500/TC500A**:  $V_{SS} = \pm 5V$ .

| Parameters                                    | <b>C</b> 11111    | T <sub>A</sub> = +25°C |      |                     | T <sub>A</sub> =   | • 0°C to 7 | '0°C                |       | Conditions                              |  |

|-----------------------------------------------|-------------------|------------------------|------|---------------------|--------------------|------------|---------------------|-------|-----------------------------------------|--|

|                                               | Sym               | Min.                   | Тур. | Max.                | Min.               | Тур.       | Max.                | Units | Conditions                              |  |

| Voltage Reference<br>Range                    | V <sub>REF</sub>  | V <sub>SS</sub> +1     | —    | V <sub>DD</sub> – 1 | V <sub>SS</sub> +1 | -          | V <sub>DD</sub> – 1 | V     | V <sub>REF</sub> - V <sub>REF</sub> +   |  |

| Digital                                       |                   |                        |      |                     |                    |            |                     |       |                                         |  |

| Comparator Logic 1,<br>Output High            | V <sub>OH</sub>   | 4                      | —    | —                   | 4                  | _          | _                   | V     | $I_{\text{SOURCE}} = 400 \ \mu\text{A}$ |  |

| Comparator Logic 0,<br>Output Low             | V <sub>OL</sub>   | —                      | —    | 0.4                 | _                  | _          | 0.4                 | V     | I <sub>SINK</sub> = 2.1 mA              |  |

| Logic 1, Input High<br>Voltage                | V <sub>IH</sub>   | 3.5                    | —    | —                   | 3.5                | _          | _                   | V     |                                         |  |

| Logic 0, Input Low<br>Voltage                 | V <sub>IL</sub>   | _                      | —    | 1                   | —                  | _          | 1                   | V     |                                         |  |

| Logic Input Current                           | ١L                | _                      |      |                     | _                  | 0.3        |                     | μA    | Logic '1' or '0'                        |  |

| Comparator Delay                              | t <sub>D</sub>    | _                      | 2    | _                   | _                  | 3          |                     | μSec  |                                         |  |

| Multiplexer (TC514 O                          | nly)              |                        |      |                     |                    |            |                     | -     | -                                       |  |

| Maximum Input<br>Voltage                      |                   | -2.5                   | —    | 2.5                 | -2.5               | _          | 2.5                 | V     | V <sub>DD</sub> = 5V                    |  |

| Drain/Source ON<br>Resistance                 | R <sub>DSON</sub> | —                      | 6    | 10                  | _                  | _          | _                   | kΩ    | V <sub>DD</sub> = 5V                    |  |

| Power (TC510/TC514                            | Only)             |                        | •    |                     |                    |            |                     |       |                                         |  |

| Supply Current                                | ۱ <sub>S</sub>    | _                      | 1.8  | 2.4                 |                    |            | 3.5                 | mA    | V <sub>DD</sub> = 5V, A = 1, B =        |  |

| Power Dissipation                             | PD                | _                      | 18   |                     | _                  | _          | _                   | mW    | $V_{DD} = 5V$                           |  |

| Positive Supply<br>Operating Voltage<br>Range | V <sub>DD</sub>   | 4.5                    | —    | 5.5                 | 4.5                | _          | 5.5                 | V     |                                         |  |

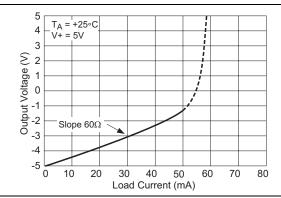

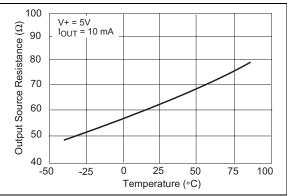

| Operating Source<br>Resistance                | R <sub>OUT</sub>  | _                      | 60   | 85                  |                    |            | 100                 | Ω     | I <sub>OUT</sub> = 10 mA                |  |

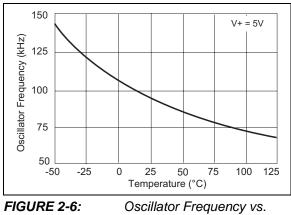

| Oscillator Frequency                          |                   | _                      | 100  | —                   | _                  | —          |                     | kHz   | Note 1                                  |  |

| Maximum Current<br>Out                        | I <sub>OUT</sub>  | _                      |      | -10                 | _                  | _          | -10                 | mA    | $V_{DD} = 5V$                           |  |

| Power (TC500/TC500                            | A Only)           |                        |      |                     |                    |            |                     |       |                                         |  |

| Supply Current                                | ۱ <sub>S</sub>    | _                      | 1    | 1.5                 | _                  | _          | 2.5                 | mA    | $V_{S} = \pm 5V, A = B = 1$             |  |

| Power Dissipation                             | PD                | _                      | 10   | _                   |                    | —          | _                   | mW    | $V_{DD} = 5V, V_{SS} = -5V$             |  |

| Positive Supply<br>Operating Range            | V <sub>DD</sub>   | 4.5                    | —    | 7.5                 | 4.5                | _          | 7.5                 | V     |                                         |  |

| Negative Supply<br>Operating Range            | V <sub>SS</sub>   | -4.5                   | —    | -7.5                | - 4.5              | —          | -7.5                | V     |                                         |  |

Note 1: Integrate time  $\geq$  66 msec, auto-zero time  $\geq$  66 msec, V<sub>INT</sub> (peak)  $\approx$  4V.

2: End point linearity at ±1/4, ±1/2, ±3/4 F.S. after full-scale adjustment.

3: Rollover error is related to  $C_{INT}$ ,  $C_{REF}$ ,  $C_{AZ}$  characteristics.

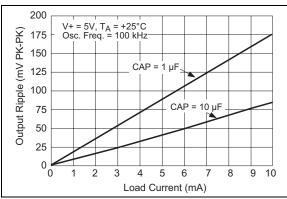

#### 2.0 **TYPICAL PERFORMANCE CURVES**

The graphs and tables provided following this note are a statistical summary based on a limited number of Note: samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

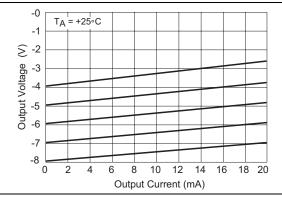

Output Voltage vs. Load

Output Ripple vs. Load

FIGURE 2-2: Current.

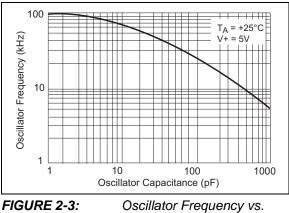

Capacitance.

FIGURE 2-4: Output Voltage vs. Output Current.

FIGURE 2-5: **Output Source Resistance** vs. Temperature.

Temperature.

#### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

#### TABLE 3-1: PIN FUNCTION TABLE

|                  | Pin No.  |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------|----------|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TC500,<br>TC500A | TC510    | TC514    | Symbol             | Function                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 1                | 2        | 2        | C <sub>INT</sub>   | Integrator output. Integrator capacitor connection.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 2                | Not Used | Not Used | V <sub>SS</sub>    | Negative power supply input (TC500/TC500A only).                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 3                | 3        | 3        | C <sub>AZ</sub>    | Auto-zero input. The auto-zero capacitor connection.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 4                | 4        | 4        | BUF                | Buffer output. The Integrator capacitor connection.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 5                | 5        | 5        | ACOM               | This pin is grounded in most applications. It is recommended that ACOM and the input common pin (Ve <sub>n</sub> - or CH <sub>n</sub> -) be within the analog Common Mode Range (CMR).                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 6                | 6        | 6        | C <sub>REF</sub> - | Input. Negative reference capacitor connection.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 7                | 7        | 7        | C <sub>REF</sub> + | Input. Positive reference capacitor connection.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 8                | 8        | 8        | V <sub>REF</sub> - | Input. External voltage reference (-) connection.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 9                | 9        | 9        | V <sub>REF</sub> + | Input. External voltage reference (+) connection.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 10               | 15       | Not Used | V <sub>IN</sub> -  | Negative analog input.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 11               | 16       | Not Used | V <sub>IN</sub> +  | Positive analog input.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 12               | 18       | 22       | A                  | Input. Converter phase control MSB. (See input B.)                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 13               | 17       | 21       | В                  | Input. Converter phase control LSB. The states of A, B place the TC5XX in one of<br>four required phases. A conversion is complete when all four phases have been<br>executed:<br>Phase control input pins: AB = 00: Integrator zero<br>01: Auto-zero<br>10: Integrate                                                                                                                                        |  |  |  |  |  |  |

|                  |          |          |                    | 11: De-integrate                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 14               | 19       | 23       | CMPTR<br>OUT       | Zero crossing comparator output. CMPTR is high during the integration phase when a <u>positive</u> input voltage is being integrated and is low when a negative input voltage is being integrated. A high-to-low transition on CMPTR signals the processor that the De-integrate phase is completed. CMPTR is undefined during the auto-zero phase. It should be monitored to time the integrator zero phase. |  |  |  |  |  |  |

| 15               | 23       | 27       | DGND               | Input. Digital ground.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 16               | 21       | 25       | V <sub>DD</sub>    | Input. Power supply positive connection.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| _                | 22       | 26       | CAP+               | Input. Negative power supply converter capacitor (+) connection.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                  | 24       | 28       | CAP-               | Input. Negative power supply converter capacitor (-) connection.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| _                | 1        | 1        | V <sub>OUT</sub>   | Output. Negative power supply converter output and reservoir capacitor connection.<br>This output can be used to power other devices in the circuit requiring a negative<br>bias voltage.                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | 20       | 24       | OSC                | Oscillator control input. The negative power supply converter normally runs at a frequency of 100 kHz. The converter oscillator frequency can be slowed down (to reduce quiescent current) by connecting an external capacitor between this pin and $V_{\text{DD}}$ (see Section 2.0 "Typical Performance Curves").                                                                                           |  |  |  |  |  |  |

|                  | —        | 18       | CH1+               | Positive analog input pin. MUX channel 1.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                |          | 13       | CH1-               | Negative analog input pin. MUX channel 1.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | —        | 17       | CH2+               | Positive analog input pin. MUX channel 2.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | _        | 12       | CH2-               | Negative analog input pin. MUX channel 2.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | _        | 16       | CH3+               | Positive analog input pin. MUX channel 3.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | _        | 11       | CH3-               | Negative analog input pin. MUX channel 3.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | _        | 15       | CH4+               | Positive analog input pin. MUX channel 4.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| _                | _        | 10       | CH4-               | Negative analog input pin. MUX channel 4                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| _                | _        | 20       | A0                 | Multiplexer input channel select input LSB (see A1).                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                  | _        | 19       | A1                 | Multiplexer input channel select input MSB.<br>Phase control input pins: A1, A0 = 00 = Channel 1<br>01 = Channel 2<br>10 = Channel 3<br>11 = Channel 4                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

#### 4.0 DETAILED DESCRIPTION

#### 4.1 Dual Slope Conversion Principles

Actual data conversion is accomplished in two phases: input signal integration and reference voltage de-integration.

The integrator output is initialized to 0V prior to the start of integration. During integration, analog switch S<sub>1</sub> connects V<sub>IN</sub> to the integrator input where it is maintained for a fixed time period (T<sub>INT</sub>). The application of V<sub>IN</sub> causes the integrator output to depart 0V at a rate determined by the *magnitude* of V<sub>IN</sub> and a direction determined by the *polarity* of V<sub>IN</sub>. The de-integration phase is initiated immediately at the expiration of T<sub>INT</sub>.

During de-integration, S1 connects a reference voltage (having a polarity opposite that of  $V_{IN}$ ) to the integrator input. At the same time, an external precision timer is started. The de-integration phase is maintained until the comparator output changes state, indicating the integrator has returned to its starting point of 0V. When this occurs, the precision timer is stopped. The de-integration time period ( $T_{DEINT}$ ), as measured by the precision timer, is directly proportional to the magnitude of the applied input voltage (see Figure 4-3).

A simple mathematical equation relates the input signal, reference voltage and integration time:

#### **EQUATION 4-1:**

$$\frac{1}{R_{INT}C_{INT}}\int_{0}^{T_{INT}}V_{IN}(T)DT = \frac{V_{REF}C_{DEINT}}{R_{INT}C_{INT}}$$

Where:

$V_{REF}$  = Reference Voltage

$T_{INT}$  = Signal Integration time (fixed)

t<sub>DEINT</sub> = Reference Voltage Integration time (variable)

For a constant VIN:

#### **EQUATION 4-2:**

$$V_{IN} = V_{REF} \frac{T_{DEINT}}{T_{INT}}$$

The dual slope converter accuracy is unrelated to the integrating resistor and capacitor values as long as they are stable during a measurement cycle.

An inherent benefit is noise immunity. Input noise spikes are integrated (averaged to zero) during the integration periods. Integrating ADCs are immune to the large conversion errors that plague successive approximation converters in high noise environments.

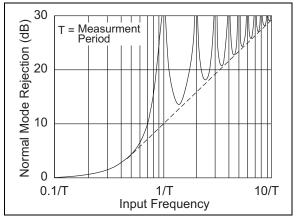

Integrating converters provide inherent noise rejection with at least a 20dB/decade attenuation rate. Interference signals with frequencies at integral multiples of the integration period are, theoretically, completely removed, since the average value of a sine wave of frequency (1/T) averaged over a period (T) is zero.

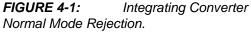

Integrating converters often establish the integration period to reject 50/60 Hz line frequency interference signals. The ability to reject such signals is shown by a normal mode rejection plot (Figure 4-1). Normal mode rejection is limited in practice to 50 to 65 dB, since the line frequency can deviate by a few tenths of a percent (Figure 4-2).

FIGURE 4-2: Line Frequency Deviation.

© 2006 Microchip Technology Inc.

FIGURE 4-3: Basic Dual Slope Converter.

#### 5.0 TC500/A/510/514 CONVERTER OPERATION

The TC500/A/510/514 incorporates an auto-zero and Integrator phase in addition to the input signal Integrate and reference De-integrate phases. The addition of these phases reduce system errors, calibration steps and shorten overrange recovery time. A typical measurement cycle uses all four phases in the following order:

- 1. Auto-zero.

- 2. Input signal integration.

- 3. Reference de-integration.

- 4. Integrator output zero.

| Conversion Phase                                  | swı    | SW <sub>R</sub> + | SW <sub>R</sub> - | swz    | SW <sub>R</sub> | SW1    | SWIZ   |

|---------------------------------------------------|--------|-------------------|-------------------|--------|-----------------|--------|--------|

| Auto-zero $(A = 0, B = 1)$                        | —      |                   |                   | Closed | Closed          | Closed |        |

| Input Signal Integration $(A = 1, B = 0)$         | Closed |                   | —                 |        |                 | —      | —      |

| Reference Voltage De-integration $(A = 1, B = 1)$ | _      | *<br>Closed       | _                 | _      | _               | Closed | _      |

| Integrator Output Zero (A = 0, B = 0)             | —      | _                 | _                 | _      | Closed          | Closed | Closed |

TABLE 5-1: INTERNAL ANALOG GATE STATUS

\* Assumes a positive polarity input signal. SW<sup>-</sup><sub>RI</sub> would be closed for a negative input signal.

#### 5.1 Auto-zero Phase (AZ)

During this phase, errors due to buffer, integrator and comparator offset voltages are nulled out by charging  $C_{AZ}$  (auto-zero capacitor) with a compensating error voltage.

The external input signal is disconnected from the internal circuitry by opening the two SW<sub>I</sub> switches. The internal input points connect to analog common. The reference capacitor is charged to the reference voltage potential through SW<sub>R</sub>. A feedback loop, closed around the integrator and comparator, charges the capacitor ( $C_{AZ}$ ) with a voltage to compensate for buffer amplifier, integrator and comparator offset voltages.

#### 5.2 Analog Input Signal Integration Phase (INT)

The TC5XX integrates the differential voltage between the V<sub>IN</sub>+ and V<sub>IN</sub>- inputs. The differential voltage must be within the device's Common mode range V<sub>CMR</sub>. The input signal polarity is normally checked via software at the end of this phase: CMPTR = 1 for positive polarity; CMPTR = 0 for negative polarity.

#### 5.3 Reference Voltage De-integration Phase (D<sub>INT</sub>)

The previously charged reference capacitor is connected with the proper polarity to ramp the integrator output back to zero. An externally-provided, precision timer is used to measure the duration of this phase. The resulting time measurement is proportional to the magnitude of the applied input voltage.

#### 5.4 Integrator Output Zero Phase (IZ)

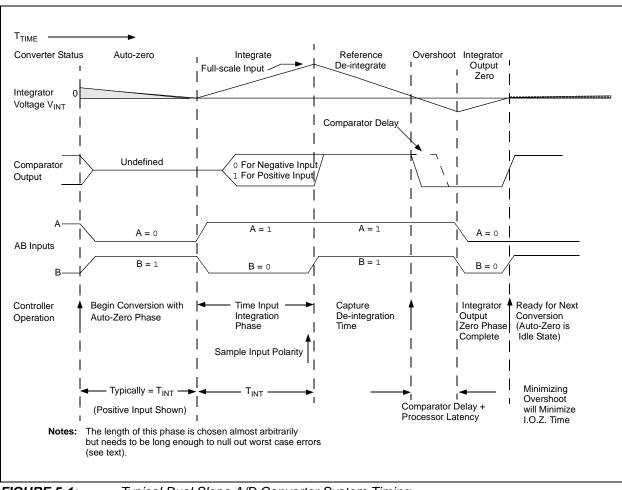

This phase ensures the integrator output is at 0V when the auto-zero phase is entered, and that only system offset voltages are compensated. This phase is used at the end of the reference voltage de-integration phase and MUST be used for ALL TC5XX applications having resolutions of 12-bits or more. If this phase is not used, the value of the auto-zero capacitor ( $C_{AZ}$ ) must be about 2 to 3 times the value of the integration capacitor ( $C_{INT}$ ) to reduce the effects of charge sharing. The integrator output zero phase should be programmed to operate until the output of the comparator returns high. The overall timing system is shown in Figure 5-1.

The internal analog switch status for each of these phases is summarized in Table 5-1. This table references the Typical Application.

## TC500/A/510/514

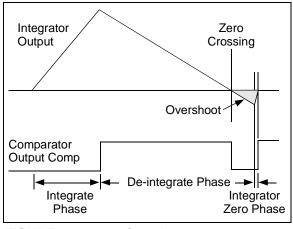

FIGURE 5-1: Typical Dual Slope A/D Converter System Timing.

#### 6.0 ANALOG SECTION

#### 6.1 Differential Inputs (V<sub>IN+</sub>, V<sub>IN</sub>-)

The TC5XX operates with differential voltages within the input amplifier Common mode range. The amplifier Common mode range extends from 1.5V below positive supply to 1.5V above negative supply. Within this Common mode voltage range, Common mode rejection is typically 80 dB. Full accuracy is maintained, however, when the inputs are no less than 1.5V from either supply.

The integrator output also follows the Common mode voltage. The integrator output must not be allowed to saturate. A worst-case condition exists, for example, when a large, positive Common mode voltage, with a near full-scale negative differential input voltage, is applied. The negative input signal drives the integrator positive when most of its swing has been used up by the positive Common mode voltage. For these critical applications, the integrator swing can be reduced. The integrator output can swing within 0.9V of either supply without loss of linearity.

#### 6.2 Analog Common

Analog common is used as  $V_{IN}$  return during system zero and reference de-integrate. If  $V_{IN}$ - is different from analog common, a Common mode voltage exists in the system. This signal is rejected by the excellent CMR of the converter. In most applications,  $V_{IN}$ - will be set at a fixed known voltage (i.e., power supply common). A Common mode voltage will exist when  $V_{IN}$ - is not connected to analog common.

## 6.3 Differential Reference (V<sub>REF</sub>+, V<sub>REF</sub>-)

The reference voltage can be anywhere within 1V of the power supply voltage of the converter. Rollover error is caused by the reference capacitor losing or gaining charge due to stray capacitance on its nodes. The difference in reference for (+) or (-) input voltages will cause a rollover error. This error can be minimized by using a large reference capacitor in comparison to the stray capacitance.

#### 6.4 Phase Control Inputs (A, B)

The A, B unlatched logic inputs select the TC5XX operating phase. The A, B inputs are normally driven by a microprocessor I/O port or external logic.

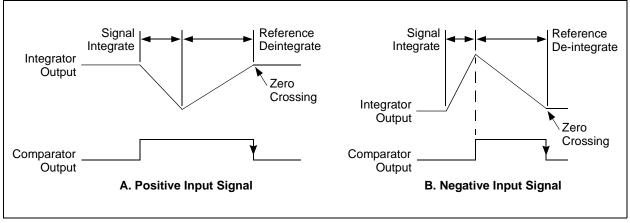

#### 6.5 Comparator Output

By monitoring the comparator output during the fixed signal integrate time, the input signal polarity can be determined by the microprocessor controlling the conversion. The comparator output is high for positive signals and low for negative signals during the signal integrate phase (see Figure 6-1).

During the reference de-integrate phase, the comparator output will make a high-to-low transition as the integrator output ramp crosses zero. The transition is used to signal the processor that the conversion is complete.

The internal comparator delay is  $2 \,\mu$ sec, typically. Figure 6-1 shows the comparator output for large positive and negative signal inputs. For signal inputs at or near zero volts, however, the integrator swing is very small. If Common mode noise is present, the comparator can switch several times during the beginning of the signal integrate period. To ensure that the polarity reading is correct, the comparator output should be read and stored at the end of the signal integrate phase.

The comparator output is undefined during the autozero phase and is used to time the integrator output zero phase. (See **Section 8.6** "**Integrator Output Zero Phase**").

#### 7.0 TYPICAL APPLICATIONS

#### 7.1 Component Value Selection

The procedure outlined below allows the user to arrive at values for the following TC5XX design variables:

- 1. Integration Phase Timing.

- 2. Integrator Timing Components (R<sub>INT</sub>, C<sub>INT</sub>).

- 3. Auto-zero and Reference Capacitors.

- 4. Voltage Reference.

#### 7.2 Select Integration Time

Integration time must be picked as a multiple of the period of the line frequency. For example,  $T_{INT}$  times of 33 msec, 66 msec and 132 msec maximize 60 Hz line rejection.

#### 7.3 DINT and IZ Phase Timing

The duration of the DINT phase is a function of the amount of voltage stored on the integrator during  $T_{INT}$  and the value of  $V_{REF}$ . The DINT phase must be initiated immediately following INT and terminated when an integrator output zero-crossing is detected. In general, the maximum number of counts chosen for DINT is twice that of INT (with  $V_{REF}$  chosen at  $V_{IN(MAX)}/2$ ).

#### 7.4 Calculate Integrating Resistor (R<sub>INT</sub>)

The desired full-scale input voltage and amplifier output current capability determine the value of  $R_{\text{INT}}$ . The buffer and integrator amplifiers each have a full-scale current of 20  $\mu A.$

The value of  $\mathsf{R}_{\mathsf{INT}}$  is, therefore, directly calculated in the following equation:

#### **EQUATION 7-1:**

$$R_{INT}(in M\Omega) = \frac{V_{IN(MAX)}}{20}$$

Where:

V<sub>IN(MAX)</sub> = Maximum input voltage (full count voltage)

$R_{INT}$  = Integrating Resistor (in M $\Omega$ )

For loop stability,  $R_{INT}$  should be  $\ge 50 \text{ k}\Omega$ .

#### 7.5 Select Reference (C<sub>REF</sub>) and Autozero (C<sub>AZ</sub>) Capacitors

$C_{REF}$  and  $C_{AZ}$  must be low leakage capacitors (such as polypropylene). The slower the conversion rate, the larger the value  $C_{REF}$  must be. Recommended capacitors for  $C_{REF}$  and  $C_{AZ}$  are shown in Table 7-1. Larger values for  $C_{AZ}$  and  $C_{REF}$  may also be used to limit rollover errors.

#### TABLE 7-1: C<sub>REF</sub> AND C<sub>AZ</sub> SELECTION

| Conversions<br>Per Second | Typical Value of<br>C <sub>REF</sub> , C <sub>AZ</sub> (μF) | Suggested* Part<br>Number |  |  |  |

|---------------------------|-------------------------------------------------------------|---------------------------|--|--|--|

| >7                        | 0.1                                                         | SMR5 104K50J01L4          |  |  |  |

| 2 to 7                    | 0.22                                                        | SMR5 224K50J02L4          |  |  |  |

| 2 or less                 | 0.47                                                        | SMR5 474K50J04L4          |  |  |  |

\* Manufactured by Evox Rifa, Inc.

#### 7.6 Calculate Integrating Capacitor (C<sub>INT</sub>)

The integrating capacitor must be selected to maximize integrator output voltage swing. The integrator output voltage swing is defined as the absolute value of V<sub>DD</sub> (or V<sub>SS</sub>) less 0.9V (i.e., IV<sub>DD</sub> - 0.9VI or IV<sub>SS</sub> + 0.9VI). Using the 20  $\mu$ A buffer maximum output current, the value of the integrating capacitor is calculated using the following equation.

#### **EQUATION 7-2:**

$$C_{INT} = \frac{(T_{INT})(20 \times 10^{-6})}{(V_{\rm S} - 0.9)}$$

Where:

T<sub>INT</sub> = Integration Period

$V_{S} = IV_{DD}I$  or  $IV_{SS}I$ , whichever is less (TC500/A)

V<sub>S</sub> = IV<sub>DD</sub>I **(TC510, TC514)**

It is critical that the integrating capacitor has a very low dielectric absorption. Polypropylene capacitors are an example of one such dialectic. Polyester and polybicarbonate capacitors may also be used in less critical applications. Table 7-2 summarizes recommended capacitors for  $C_{\rm INT}$ .

TABLE 7-2: RECOMMENDED CAPACITOR FOR C<sub>INT</sub>

| Value | Suggested<br>Part Number* |  |  |  |  |  |  |  |

|-------|---------------------------|--|--|--|--|--|--|--|

| 0.1   | SMR5 104K50J01L4          |  |  |  |  |  |  |  |

| 0.22  | SMR5 224K50J02L4          |  |  |  |  |  |  |  |

| 0.33  | SMR5 334K50J03L4          |  |  |  |  |  |  |  |

| 0.47  | SMR5 474K50J04L4          |  |  |  |  |  |  |  |

\* Manufactured by Evox Rifa, Inc.

#### 7.7 Calculate V<sub>REF</sub>

The reference de-integration voltage is calculated using the following equation:

#### **EQUATION 7-3:**

$$V_{REF} = \frac{(V_{S} - 0.9)(C_{INT})(R_{INT})}{2(R_{INT})}V$$

#### 8.0 DESIGN CONSIDERATIONS

#### 8.1 Noise

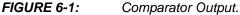

The threshold noise (N<sub>TH</sub>) is the algebraic sum of the integrator and comparator noise and is typically 30  $\mu$ V. Figure 8-1 illustrates how the value of the reference voltage can affect the final count. Such errors can be reduced by increased integration times, in the same way that 50/60 Hz noise is rejected. The signal-to-noise ratio is related to the integration time (T<sub>INT</sub>) and the integration time constant (R<sub>INT</sub>, C<sub>INT</sub>) as follows:

#### **EQUATION 8-1:**

$$S/N(dB) = 20 \log\left(\frac{V_{IN}}{30 \times 10^{-6}} \bullet \frac{t_{INT}}{(R_{INT}) \bullet (C_{INT})}\right)$$

#### 8.2 System Timing

To obtain maximum performance from the TC5XX, the overshoot at the end of the de-integration phase must be minimized. Also, the integrator output zero phase must be terminated as soon as the comparator output returns high (see Figure 5-1).

Figure 5-1 shows the overall timing for a typical system in which a TC5XX is interfaced to a microcontroller. The microcontroller drives the A, B inputs with I/O lines and monitors the comparator output (CMPTR) using an I/O line or dedicated timer capture control pin. It may be necessary to monitor the state of the CMPTR output in addition to having it control a timer directly for the Reference de-integration phase (this is further explained below.)

The timing diagram in Figure 5-1 is not to scale, as the timing in a real system depends on many system parameters and component value selections. There are four critical timing events (as shown in Figure 5-1): sampling the input polarity, capturing the de-integration time, minimizing overshoot and properly executing the integrator output zero phase.

#### 8.3 Auto-zero Phase

The length of this phase is usually set to be equal to the input signal integration time. This decision is virtually arbitrary since the magnitudes of the various system errors are not known. Setting the auto-zero time equal to the Input Integrate time should be more than adequate to null out system errors. The system may remain in this phase indefinitely (i.e., auto-zero is the appropriate Idle state for a TC5XX device).

#### 8.4 Input Signal Integrate Phase

The length of this phase is constant from one conversion to the next and depends on system parameters and component value selections. The calculation of  $T_{INT}$  is shown elsewhere in this data sheet. At some point near the end of this phase, the microcontroller should sample CMPTR to determine the input signal polarity. This value is, in effect, the Sign Bit for the overall conversion result. Optimally, CMPTR should be sampled just <u>before</u> this phase is terminated by changing AB from 10 to 11. The consideration here is that, during the initial stage of input integration when the integrator voltage is low, the comparator may be affected by noise and its output unreliable. Once integration is well underway, the comparator will be in a defined state.

#### 8.5 Reference De-integration

The length of this phase must be precisely measured from the transition of AB from 10 to 11 to the fallingedge of CMPTR. The comparator delay contributes some error in timing this phase. The typical delay is specified to be 2  $\mu$ sec. This should be considered in the context of the length of a single count when determining overall system performance and possible single count errors. Additionally, overshoot will result in charge accumulating on the integrator once its output crosses zero. This charge must be nulled during the integrator output zero phase.

## TC500/A/510/514

#### 8.6 Integrator Output Zero Phase

The comparator delay and the controller's response latency may result in overshoot, causing charge buildup on the integrator at the end of a conversion. This charge must be removed or performance will degrade. The integrator output zero phase should be activated (AB = 00) until CMPTR goes high. It is absolutely critical that this phase be terminated immediately so that overshoot is not allowed to occur in the opposite direction. At this point, it can be assured that the integrator is near zero. Auto-zero should be entered (AB = 01) and the TC5XX held in this state until the next cycle is begun (see Figure 8-2).

FIGURE 8-2: Overshoot.

#### 8.7 Using the TC510/TC514

#### 8.7.1 NEGATIVE SUPPLY VOLTAGE CONVERTER (TC510, TC514)

A capacitive charge pump is employed to invert the voltage on  $V_{DD}$  for negative bias within the TC510/TC514. This voltage is also available on the  $V_{OUT}$  pin to provide negative bias elsewhere in the system. Two external capacitors are required to perform the conversion.

Timing is generated by an internal state machine driven from an on-board oscillator. During the first phase, capacitor  $C_F$  is switched across the power supply and charged to  $V_{S^+}$ . This charge is transferred to capacitor  $C_{OUT^-}$  during the second phase. The oscillator normally runs at 100 kHz to ensure minimum output ripple. This frequency can be reduced by placing a capacitor from OSC to  $V_{DD}$ . The relationship between the capacitor value is shown in **Section 2.0 "Typical Performance Curves"**.

#### 8.7.2 ANALOG INPUT MULTIPLEXER (TC514)

The TC514 is equipped with a four-input differential analog multiplexer. Input channels are selected using select inputs (A1, A0). These are high-true control signals (i.e., channel 0 is selected when (A1, A0 = 00).

#### 9.0 DESIGN EXAMPLES

| Refer to F | igures 9-1 to 9-4.                                                                                   |

|------------|------------------------------------------------------------------------------------------------------|

| Given:     | Required Resolution: 16 bits (65,536 counts).                                                        |

|            | Maximum V <sub>IN</sub> : ±2V                                                                        |

|            | Power Supply Voltage: +5V                                                                            |

|            | 60 Hz System                                                                                         |

| Step 1.    | Pick integration time (t <sub>INT</sub> ) as a multiple of the line frequency:                       |

|            | 1/60 Hz = 16.6 msec. Use 4x line<br>frequency.                                                       |

|            | = 66 msec                                                                                            |

| Step 2.    | Calculate R <sub>INT</sub> :                                                                         |

|            | R <sub>INT</sub> = V <sub>IN(MAX)</sub> /20 μA 2 /20 μA<br>= 100 kΩ                                  |

| Step 3.    | Calculate C <sub>INT</sub> for maximum (4V) integrator output swing.                                 |

|            | $C_{INT} = (t_{INT}) (20 \times 10^{-6}) / (V_S - 0.9)$<br>= (.066) (20 × 10 <sup>-6</sup> ) / (4.1) |

|            | = 0.32 $\mu$ F (use closest value: 0.33 $\mu$ F)                                                     |

| Note:      | Microchip recommended capacitor:<br>Evox Rifa p/n: 5MR5 334K50J03L4.                                 |

| Step 4.    | Choose $C_{REF}$ and $C_{AZ}$ based on conversion rate.                                              |

|            | Conversions/sec:                                                                                     |

|            | = $1/(T_{AZ} + T_{INT} + 2 T_{INT} + 2 msec)$                                                        |

|            | = 1/(66  msec  +66  msec)                                                                            |

|            | +132 msec +2 msec)<br>= 3.7 conversions/sec                                                          |

|            | From which $C_{AZ} = C_{REF} = 0.22 \mu\text{F}$<br>(see Table 7-1)                                  |

| Note:      | Microchip recommended capacitor:<br>Evox Rifa p/n: 5MR5 224K50J02L4                                  |

| Step 5.    | Calculate V <sub>REF</sub> :                                                                         |

EQUATION 9-1:

$$V_{REF} = \frac{(V_S - 0.9)(C_{IN})}{2(T_{V_S} - 0.9)}$$

$$= \frac{(V_S - 0.9)(C_{INT})(R_{INT})}{2(T_{INT})}$$

= (4.1)(0.33 × 1<sup>-6</sup>)(10<sup>5</sup>)

2(0.66)

= 1.025

TC510 Design Sample.

TC514 Design Example.

### TC500/A/510/514

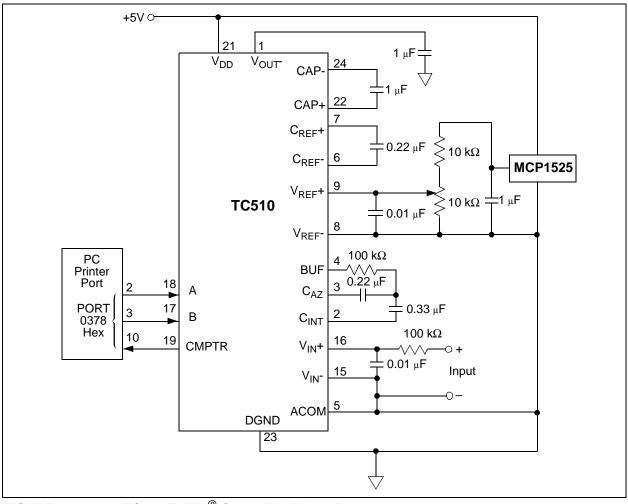

FIGURE 9-3: TC510 To IBM<sup>®</sup> Compatible Printer Port.

## TC500/A/510/514

FIGURE 9-4: TC514 To IBM<sup>®</sup> Compatible Printer Port.

#### **10.0 PACKAGING INFORMATION**

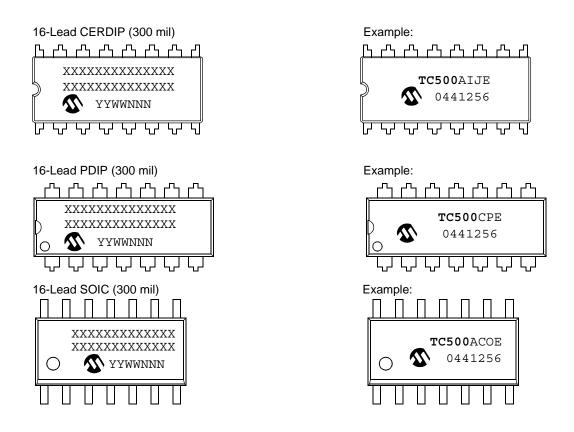

#### **10.1** Package Marking Information

| Legend: | XXX<br>YY<br>WW<br>NNN | Customer specific information*<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|---------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | d over to t            | nt the full Microchip part number cannot be marked on one line, it will<br>he next line thus limiting the number of available characters for cus-<br>mation. |

\* Standard marking consists of Microchip part number, year code, week code, traceability code. For marking beyond this, certain price adders apply. Please check with your Microchip Sales Office.

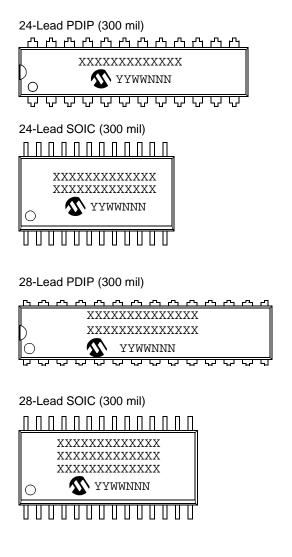

#### Package Marking Information (Continued)

Example:

Example:

#### Example:

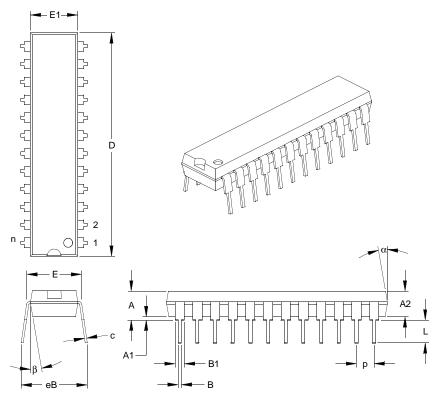

#### 16-Lead Ceramic Dual In-line (JE) – 300 mil (CERDIP)

|                            | Units    |      |      |      | MILLIMETERS |       |       |

|----------------------------|----------|------|------|------|-------------|-------|-------|

| Dimensior                  | n Limits | MIN  | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n        |      | 18   |      |             | 18    |       |

| Pitch                      | р        |      | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | Α        | .160 | .180 | .200 | 4.06        | 4.57  | 5.08  |

| Standoff §                 | A1       | .015 | .030 | .040 | 0.38        | 0.76  | 1.02  |

| Shoulder to Shoulder Width | E        | .290 | .305 | .325 | 7.37        | 7.75  | 8.25  |

| Ceramic Pkg. Width         | E1       | .280 | .288 | .296 | 7.11        | 7.32  | 7.52  |

| Overall Length             | D        | .752 | .760 | .780 | 19.10       | 19.30 | 19.81 |

| Tip to Seating Plane       | L        | .125 | .163 | .200 | 3.18        | 4.14  | 5.08  |

| Lead Thickness             | С        | .008 | .012 | .014 | 0.20        | 0.30  | 0.36  |

| Upper Lead Width           | B1       | .045 | .055 | .065 | 1.14        | 1.40  | 1.65  |

| Lower Lead Width           | В        | .015 | .018 | .021 | 0.38        | 0.46  | 0.53  |

| Overall Row Spacing        | eB       | .325 | .360 | .410 | 8.25        | 9.14  | 10.41 |

| *O ta - III'a D            |          |      |      |      |             | •     |       |

\*Controlling Parameter

JEDEC Equivalent: MS-030

Drawing No. C04-003

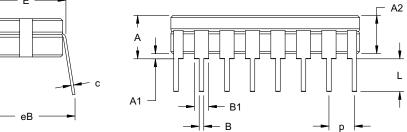

#### 16-Lead Plastic Dual In-line (PE) – 300 mil (PDIP)

|               | Units   |           | INCHES*    |            | MILLIMETERS |       |            |

|---------------|---------|-----------|------------|------------|-------------|-------|------------|

| Dimension Lim | its     | MIN       | NOM        | MAX        | MIN         | NOM   | MAX        |

|               | n       |           | 16         |            |             | 16    |            |

|               | р       |           | .100       |            |             | 2.54  |            |

| ne            | А       | .140      | .155       | .170       | 3.56        | 3.94  | 4.32       |

| hickness      | A2      | .115      | .130       | .145       | 2.92        | 3.30  | 3.68       |

| ane           | A1      | .015      |            |            | 0.38        |       |            |

| ler Width     | Е       | .300      | .313       | .325       | 7.62        | 7.94  | 8.26       |

| Vidth         | E1      | .240      | .250       | .260       | 6.10        | 6.35  | 6.60       |

|               | D       | .740      | .750       | .760       | 18.80       | 19.05 | 19.30      |

| ie            | L       | .125      | .130       | .135       | 3.18        | 3.30  | 3.43       |

|               | с       | .008      | .012       | .015       | 0.20        | 0.29  | 0.38       |

|               | B1      | .045      | .058       | .070       | 1.14        | 1.46  | 1.78       |

|               | В       | .014      | .018       | .022       | .036        | 0.46  | 0.56       |

| ng            | eB      | .310      | .370       | .430       | 7.87        | 9.40  | 10.92      |

| ор            | α       | 5         | 10         | 15         | 5           | 10    | 15         |

| ottom         | β       | 5         | 10         | 15         | 5           | 10    | 15         |

| ор            | eB<br>α | .310<br>5 | .370<br>10 | .430<br>15 | 7.87<br>5   |       | 9.40<br>10 |

\* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001

Drawing No. C04-017

Revised 07-21-05

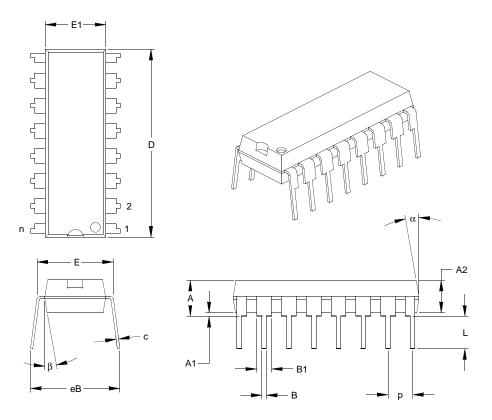

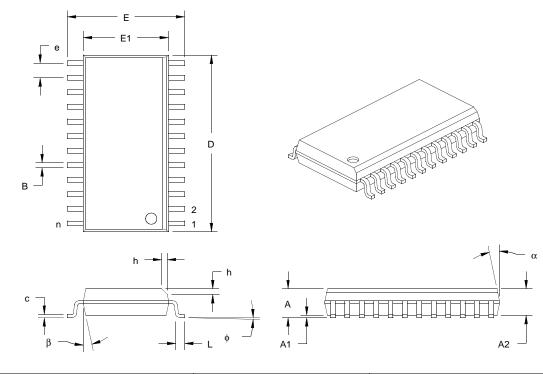

#### 16-Lead Plastic Small Outline (OE) – Wide, 300 mil (SOIC)

|                          | Units          |      | INCHES* |      | N     | MILLIMETERS |       |  |

|--------------------------|----------------|------|---------|------|-------|-------------|-------|--|

| Dir                      | nension Limits | MIN  | NOM     | MAX  | MIN   | NOM         | MAX   |  |

| Number of Pins           | n              |      | 16      |      |       | 16          | -     |  |

| Pitch                    | р              |      | .050    |      |       | 1.27        |       |  |

| Overall Height           | А              | .093 | .099    | .104 | 2.36  | 2.50        | 2.64  |  |

| Molded Package Thickness | s A2           | .088 | .091    | .094 | 2.24  | 2.31        | 2.39  |  |

| Standoff                 | § A1           | .004 | .008    | .012 | 0.10  | 0.20        | 0.30  |  |

| Overall Width            | E              | .394 | .407    | .420 | 10.01 | 10.34       | 10.67 |  |

| Molded Package Width     | E1             | .291 | .295    | .299 | 7.39  | 7.49        | 7.59  |  |

| Overall Length           | D              | .398 | .406    | .413 | 10.10 | 10.30       | 10.49 |  |

| Chamfer Distance         | h              | .010 | .020    | .029 | 0.25  | 0.50        | 0.74  |  |

| Foot Length              | L              | .016 | .033    | .050 | 0.41  | 0.84        | 1.27  |  |

| Foot Angle               | ¢              | 0    | 4       | 8    | 0     | 4           | 8     |  |

| Lead Thickness           | С              | .009 | .011    | .013 | 0.23  | 0.28        | 0.33  |  |

| Lead Width               | В              | .014 | .017    | .020 | 0.36  | 0.42        | 0.51  |  |

| Mold Draft Angle Top     | α              | 0    | 12      | 15   | 0     | 12          | 15    |  |

| Mold Draft Angle Bottom  | β              | 0    | 12      | 15   | 0     | 12          | 15    |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-102

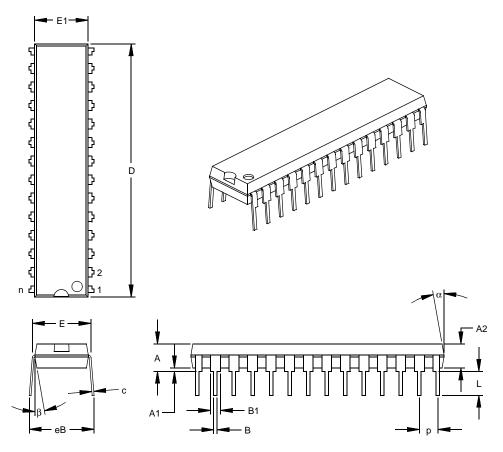

#### 24-Lead Skinny Plastic Dual In-line (PF) – 300 mil (PDIP)

|                            | Units |       | INCHES* |       | N     |       |       |

|----------------------------|-------|-------|---------|-------|-------|-------|-------|

| Dimension Limits           |       | MIN   | NOM     | MAX   | MIN   | NOM   | MAX   |

| Number of Pins             | n     |       | 24      |       |       | 24    |       |

| Pitch                      | р     |       | .100    |       |       | 2.54  |       |

| Top to Seating Plane       | А     | .140  | .150    | .160  | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2    | .115  | .130    | .145  | 2.92  | 3.30  | 3.68  |

| Base to Seating Plane      | A1    | .015  |         |       | 0.38  |       |       |

| Shoulder to Shoulder Width | E     | .295  | .310    | .325  | 7.49  | 7.87  | 8.26  |

| Molded Package Width       | E1    | .240  | .250    | .260  | 6.10  | 6.35  | 6.60  |

| Overall Length             | D     | 1.245 | 1.250   | 1.255 | 31.62 | 31.75 | 31.88 |

| Tip to Seating Plane       | L     | .120  | .125    | .130  | 3.05  | 3.18  | 3.30  |

| Lead Thickness             | с     | .008  | .012    | .015  | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1    | .045  | .053    | .060  | 1.14  | 1.33  | 1.52  |

| Lower Lead Width           | В     | .014  | .018    | .022  | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing        | eB    | .310  | .370    | .430  | 7.87  | 9.40  | 10.92 |

| Mold Draft Angle Top       | α     | 5     | 10      | 15    | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β     | 5     | 10      | 15    | 5     | 10    | 15    |

\* Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 AF

Drawing No. C04-043

Revised 09-14-05

#### 24-Lead Plastic Small Outline (OG) – Wide, 300 mil (SOIC)

|                          | Units | INCHES   |          | MILLIMETERS* |           |          |      |

|--------------------------|-------|----------|----------|--------------|-----------|----------|------|

| Dimension Lim            | its   | MIN      | NOM      | MAX          | MIN       | NOM      | MAX  |

| Number of Pins           | n     |          | 24       |              |           | 24       |      |

| Pitch                    | е     | .050 BSC |          | 1.27 BSC     |           |          |      |

| Overall Height           | А     | .093     |          | .104         | 2.35      |          | 2.65 |

| Molded Package Thickness | A2    | .081     | -        | .100         | 2.05      |          | 2.55 |

| Standoff                 | A1    | .004     |          | .012         | 0.10      |          | 0.30 |

| Overall Width            | Е     | .406 BSC |          |              | 10.30 BSC |          |      |

| Molded Package Width     | E1    |          | .295 BSC | BSC 7.50 BSC |           | 7.50 BSC |      |

| Overall Length           | D     | .607 BSC |          | 15.40 BSC    |           |          |      |

| Chamfer Distance         | h     | .010     |          | .030         | 0.25      |          | 0.75 |

| Foot Length              | L     | .016     |          | .050         | 0.40      |          | 1.27 |

| Foot Angle               | φ     | 0°       |          | 8°           | 0°        |          | 8°   |

| Lead Thickness           | С     | .008     |          | .013         | 0.20      |          | 0.33 |

| Lead Width               | В     | .012     | -        | .020         | 0.31      |          | 0.51 |

| Mold Draft Angle Top     | α     | 5°       | -        | 15°          | 5°        |          | 15°  |

| Mold Draft Angle Bottom  | β     | 5°       | -        | 15°          | 5°        |          | 15°  |

\* Controlling Parameter per JEDEC MS-103 Revision C.

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

See ASME Y14.5M JEDEC Equivalent: MS-013 AD

Drawing No. C04-025

Revised 07-19-05

28-Lead Skinny Plastic Dual In-line (PJ) – 300 mil (PDIP)

|                            | Units  |       | INCHES* |       | Ν     | IILLIMETERS |       |

|----------------------------|--------|-------|---------|-------|-------|-------------|-------|

| Dimension                  | Limits | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |

| Number of Pins             | n      |       | 28      |       |       | 28          |       |

| Pitch                      | р      |       | .100    |       |       | 2.54        |       |

| Top to Seating Plane       | А      | .140  | .150    | .160  | 3.56  | 3.81        | 4.06  |

| Molded Package Thickness   | A2     | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Base to Seating Plane      | A1     | .015  |         |       | 0.38  |             |       |

| Shoulder to Shoulder Width | Е      | .300  | .310    | .325  | 7.62  | 7.87        | 8.26  |

| Molded Package Width       | E1     | .275  | .285    | .295  | 6.99  | 7.24        | 7.49  |

| Overall Length             | D      | 1.345 | 1.365   | 1.385 | 34.16 | 34.67       | 35.18 |

| Tip to Seating Plane       | L      | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Lead Thickness             | С      | .008  | .012    | .015  | 0.20  | 0.29        | 0.38  |

| Upper Lead Width           | B1     | .040  | .053    | .065  | 1.02  | 1.33        | 1.65  |

| Lower Lead Width           | В      | .016  | .019    | .022  | 0.41  | 0.48        | 0.56  |

| Overall Row Spacing §      | eB     | .320  | .350    | .430  | 8.13  | 8.89        | 10.92 |

| Mold Draft Angle Top       | α      | 5     | 10      | 15    | 5     | 10          | 15    |

| Mold Draft Angle Bottom    | β      | 5     | 10      | 15    | 5     | 10          | 15    |

\* Controlling Parameter

\$ Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

IFDED Environment MO 2025 JEDEC Equivalent: MO-095 Drawing No. C04-070

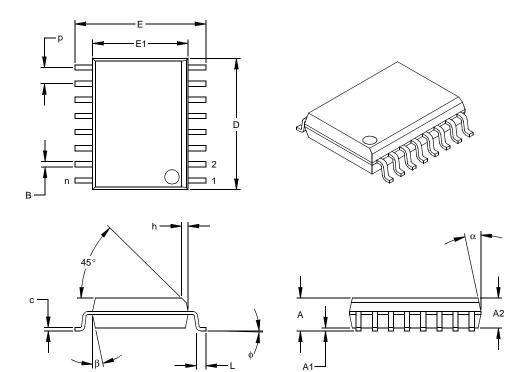

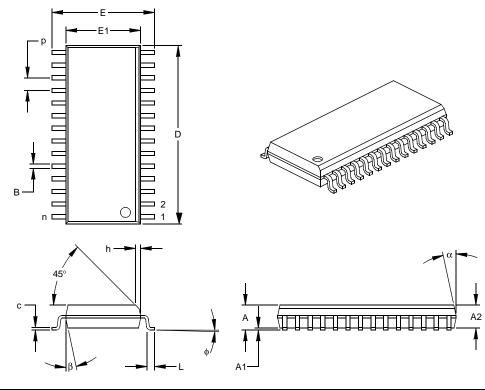

#### 28-Lead Plastic Small Outline (OI) – Wide, 300 mil (SOIC)

|                          | Units  | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|--------|---------|------|-------------|-------|-------|-------|

| Dimension                | Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n      |         | 28   |             |       | 28    |       |

| Pitch                    | р      |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α      | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2     | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1     | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | Е      | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1     | .288    | .295 | .299        | 7.32  | 7.49  | 7.59  |

| Overall Length           | D      | .695    | .704 | .712        | 17.65 | 17.87 | 18.08 |

| Chamfer Distance         | h      | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L      | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle Top           | ¢      | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С      | .009    | .011 | .013        | 0.23  | 0.28  | 0.33  |

| Lead Width               | В      | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0     | 12    | 15    |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-052

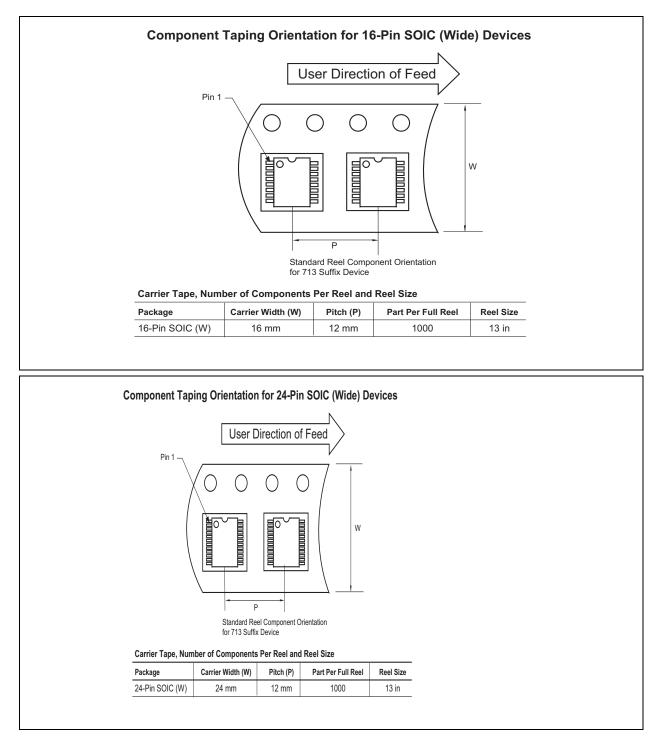

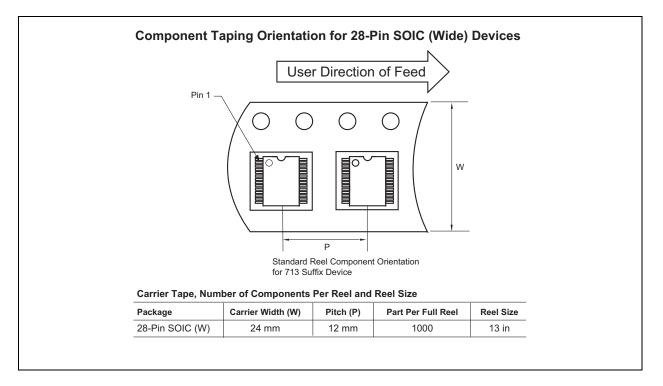

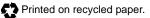

#### 10.2 Product Tape and Reel Specifications

#### **Product Tape and Reel Specifications (Continued)**

NOTES:

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | x <u>/xx</u>                                                                                                   | Exa | amples:       |                                                           |

|-------------------|----------------------------------------------------------------------------------------------------------------|-----|---------------|-----------------------------------------------------------|

| Device            | Temperature Package<br>Range                                                                                   | a)  | TC500ACOE:    | Commercial Temp.,<br>16LD SOIC package.                   |

|                   |                                                                                                                | b)  | TC500ACOE713: | Commercial Temp.,<br>16LD SOIC package,<br>Tape and Reel. |

| Device            | TC500 16 Bit Analog Processor<br>TC500A 16 Bit Analog Processor                                                | c)  | TC500ACPE:    | Commercial Temp.,<br>16LD PDIP package.                   |

|                   | TC510Precision Analog Front EndTC514Precision Analog Front End                                                 | d)  | TC500AIJE:    | Industrial Temp.,<br>16LD CERDIP package.                 |

| Temperature Range | $C = 0^{\circ}C$ to +70°C (Commercial)                                                                         | a)  | TC500COE:     | Commercial Temp.,<br>16LD SOIC package.                   |

| Tomporator Range  | I = $-25^{\circ}$ C to $+85^{\circ}$ C (Industrial)                                                            | b)  | TC500COE713:  | Commercial Temp.,<br>16LD SOIC package,<br>Tape and Reel. |

| Package:          | JE = Ceramic Dual In-line, (300 mil Body), 16-lead<br>PE = Plastic DIP, (300 mil Body), 16-lead                | c)  | TC500CPE:     | Commercial Temp.,<br>16LD PDIP package.                   |

|                   | OE = Plastic SOIC, (300 mil Body), 16-lead<br>OE713 = Plastic SOIC, (300 mil Body), 16-lead<br>(Tape and Reel) | d)  | TC500IJE:     | Industrial Temp.,<br>16LD CERDIP package.                 |

|                   | OG = Plastic DIP, (300 mil Body), 24-lead                                                                      | a)  | TC510COG:     | Commercial Temp.,<br>24LD PDIP package.                   |

|                   | OG713 = Plastic SOIC, (300 mil Body), 24-lead<br>(Tape and Reel)<br>PJ = Plastic DIP, (300 mil Body), 28-lead  | b)  | TC510COG713:  | Commercial Temp.,<br>24LD PDIP package,<br>Tape and Reel. |

|                   | OI = Plastic SOIC, (300 mil Body), 28-lead<br>OI713 = Plastic SOIC, (300 mil Body), 28-lead<br>(Tape and Reel) | c)  | TC510CPF:     | Commercial Temp.,<br>24LD PDIP package.                   |

|                   |                                                                                                                | a)  | TC514COI:     | Commercial Temp.,<br>28LD PDIP package.                   |

|                   |                                                                                                                | b)  | TC514COI713:  | Commercial Temp.,<br>28LD PDIP package,<br>Tape and Reel. |

|                   |                                                                                                                | c)  | TC514CPJ:     | Commercial Temp.,<br>28LD PDIP package.                   |

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.